## MT8332N5

# **30V/25A Complementary Enhancement Mode Field Effect Transistor**

## **General Description**

The MT8332N5 uses advanced trench technology MOSFETs to provide excellent  $R_{\text{DS(ON)}}$  and low gate charge. The complementary MOSFETs may be used in H-bridge, Inverters and other applications.

#### **Features**

$\begin{array}{ll} \text{N-channel} & \text{P-channel} \\ \text{V}_{\text{DS}} \left( \text{V} \right) = 30 \text{V} & -30 \text{V} \\ \end{array}$

$I_D = 25A (V_{GS}=10V)$  -25A  $(V_{GS} = -10V)$

$R_{DS(ON)}$   $R_{DS(ON)}$

=10 m  $\Omega(V_{GS}$ =10V) =10.5m $\Omega$  ( $V_{GS}$  = -10V) =16 m $\Omega(V_{GS}$ =4.5V) =17m $\Omega(V_{GS}$  = -4.5V)

100% Rg tested

http://www.mtsemi.com

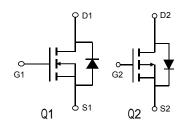

## **Simplified Schematic**

MARKING DIAGRAM & PIN ASSIGNMENT

DFN5X6-8L

Top View

| S1 [ ¹ ●                               | 8 D  |

|----------------------------------------|------|

| G1 [ <sup>2</sup><br>S2 [ <sup>3</sup> | 7 D1 |

| S2 🛚 3                                 | 6 D2 |

| G2 [ 4                                 | 5 D2 |

|                                        |      |

| Absolute Maximum Ratings T <sub>A</sub> =25°C unless otherwise noted |                       |                                   |               |     |       |  |  |

|----------------------------------------------------------------------|-----------------------|-----------------------------------|---------------|-----|-------|--|--|

| Parameter                                                            |                       | Symbol                            | Max Q1 Max Q2 |     | Units |  |  |

| Drain-Source Voltage                                                 |                       | V <sub>DS</sub>                   | 30            | -30 | V     |  |  |

| Gate-Source Voltage                                                  |                       | $V_{GS}$                          | ±20           | ±20 | V     |  |  |

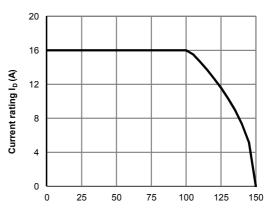

| Continuous Drain T <sub>C</sub> =25°C                                |                       | 1                                 | 25            | -25 |       |  |  |

| Current                                                              | T <sub>C</sub> =100°C | I <sub>D</sub>                    | 20            | -20 | Α     |  |  |

| Pulsed Drain Current                                                 |                       | I <sub>DM</sub>                   | 90            | -90 |       |  |  |

| Pulsed Drain Current                                                 | T <sub>A</sub> =25°C  | 1.                                | 90            | -90 | А     |  |  |

| Puised Diain Current                                                 | T <sub>A</sub> =70°C  | I <sub>DSM</sub>                  | 70            | -70 | A     |  |  |

| Avalanche Current                                                    |                       | I <sub>AS</sub>                   | 24            | 23  | Α     |  |  |

| Avalanche energy                                                     | L=0.3mH               | E <sub>AS</sub>                   | 90            | 86  | mJ    |  |  |

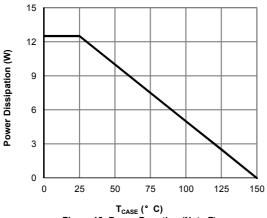

|                                                                      | T <sub>C</sub> =25°C  | $-P_{D}$                          | 12.5          | 11  | W     |  |  |

| Power Dissipation                                                    | T <sub>C</sub> =100°C | ' D                               | 5             | 4   | VV    |  |  |

| T <sub>A</sub> =25°C                                                 |                       | P <sub>DSM</sub>                  | 3.3           | 2.8 | W     |  |  |

| Power Dissipation                                                    | T <sub>A</sub> =70°C  | ' DSM                             | 2.2           | 1.9 | VV    |  |  |

| Junction and Storage Temperature Range                               |                       | T <sub>J</sub> , T <sub>STG</sub> | -55 to 150    |     | °C    |  |  |

| Thermal Characteristics     |              |                      |        |        |        |        |       |

|-----------------------------|--------------|----------------------|--------|--------|--------|--------|-------|

| Parameter                   |              | Symbol               | Typ Q1 | Typ Q2 | Max Q1 | Max Q2 | Units |

| Maximum Junction-to-Ambient | t ≤ 10s      | $R_{\theta JA}$      | 25     | 20     | 35     | 30     | °C/W  |

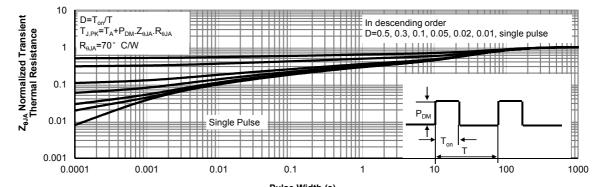

| Maximum Junction-to-Ambient | Steady-State | $\kappa_{\theta JA}$ | 50     | 48     | 70     | 65     | °C/W  |

| Maximum Junction-to-Case    | Steady-State | $R_{\theta JC}$      | 7      | 3.5    | 10     | 4.2    | °C/W  |

#### Q1 Electrical Characteristics (T<sub>J</sub>=25°C unless otherwise noted)

| Symbol                 | Parameter                          | Conditions                                                                   |                       | Min | Тур | Max  | Units |

|------------------------|------------------------------------|------------------------------------------------------------------------------|-----------------------|-----|-----|------|-------|

| STATIC F               | PARAMETERS                         |                                                                              |                       |     |     |      |       |

| BV                     | Drain-Source Breakdown Voltage     | ID=250μA, VGS=0V                                                             |                       | 30  |     |      | V     |

| I <sub>DSS</sub>       | Zero Gate Voltage Drain Current    | V <sub>DS</sub> =30V, V <sub>GS</sub> =0V                                    |                       |     | 1   | μA   |       |

| טאטי                   | Zero Gate Voltage Drain Gurrent    |                                                                              | T <sub>J</sub> =55°C  |     |     | 5    | μΑ    |

| $I_{GSS}$              | Gate-Body leakage current          | $V_{DS}$ =0V, $V_{GS}$ =±20V                                                 |                       |     |     | ±100 | nA    |

| $V_{GS(th)}$           | Gate Threshold Voltage             | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$                                           |                       | 1.0 | 1.5 | 2.5  | V     |

|                        |                                    | $V_{GS}$ =10V, $I_D$ =5A                                                     |                       |     | 10  | 15   | mΩ    |

| R <sub>DS(ON)</sub>    | Static Drain-Source On-Resistance  |                                                                              | T <sub>J</sub> =125°C |     | 15  | 22   | 11152 |

|                        |                                    | $V_{GS}$ =4.5V, $I_D$ =5A                                                    |                       |     | 16  | 23   | mΩ    |

| <b>g</b> <sub>FS</sub> | Forward Transconductance           | $V_{DS}$ =5V, $I_{D}$ =5A                                                    |                       |     | 43  |      | S     |

| $V_{SD}$               | Diode Forward Voltage              | I <sub>S</sub> =1A,V <sub>GS</sub> =0V                                       |                       |     | 0.7 | 1.3  | V     |

| Is                     | Maximum Body-Diode Continuous Cur  | rent                                                                         |                       |     |     | 20   | Α     |

| DYNAMIC                | PARAMETERS                         |                                                                              |                       |     |     |      |       |

| C <sub>iss</sub>       | Input Capacitance                  |                                                                              |                       |     | 760 |      | pF    |

| Coss                   | Output Capacitance                 | $V_{GS}$ =0V, $V_{DS}$ =15V, f=1MHz                                          |                       |     | 125 |      | pF    |

| $C_{rss}$              | Reverse Transfer Capacitance       |                                                                              |                       | 70  |     | pF   |       |

| $R_g$                  | Gate resistance                    | f=1MHz                                                                       |                       | 8.0 | 1.6 | 2.4  | Ω     |

| SWITCHI                | NG PARAMETERS                      |                                                                              |                       |     |     |      |       |

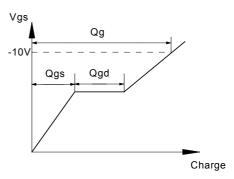

| $Q_g(10V)$             | Total Gate Charge                  |                                                                              |                       |     | 14  | 20   | nC    |

| Q <sub>g</sub> (4.5V)  | Total Gate Charge                  | V <sub>GS</sub> =10V, V <sub>DS</sub> =15V, I <sub>I</sub>                   | .=8A                  |     | 6.6 | 10   | nC    |

| $Q_{gs}$               | Gate Source Charge                 |                                                                              | _                     |     | 2.4 |      | nC    |

| $Q_{gd}$               | Gate Drain Charge                  |                                                                              |                       |     | 3   |      | nC    |

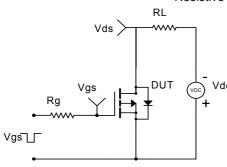

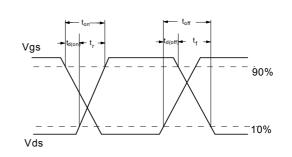

| t <sub>D(on)</sub>     | Turn-On DelayTime                  |                                                                              |                       |     | 4.4 |      | ns    |

| t <sub>r</sub>         | Turn-On Rise Time                  | $V_{GS}$ =10V, $V_{DS}$ =15V, $R_{L}$ =1.25 $\Omega$ , $R_{GEN}$ =3 $\Omega$ |                       |     | 9   |      | ns    |

| t <sub>D(off)</sub>    | Turn-Off DelayTime                 |                                                                              |                       |     | 17  |      | ns    |

| t <sub>f</sub>         | Turn-Off Fall Time                 |                                                                              |                       |     | 6   |      | ns    |

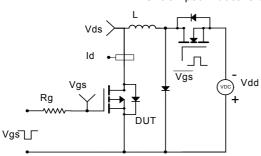

| t <sub>rr</sub>        | Body Diode Reverse Recovery Time   | I <sub>F</sub> =12A, di/dt=500A/μs                                           | 3                     |     | 7   |      | ns    |

| Q <sub>rr</sub>        | Body Diode Reverse Recovery Charge | l <sub>F</sub> =12A, di/dt=500A/με                                           | 3                     |     | 8   | _    | nC    |

A. The value of  $R_{\theta JA}$  is measured with the device mounted on 1in² FR-4 board with 2oz. Copper, in a still air environment with  $T_A$  =25° C. The Power dissipation  $P_{DSM}$  is based on  $R_{\theta JA}$  t≤ 10s and the maximum allowed junction temperature of 150° C. The value in any given application depends on

2

the user's specific board design.

B. The power dissipation P<sub>D</sub> is based on T<sub>J(MAX)</sub>=150° C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.

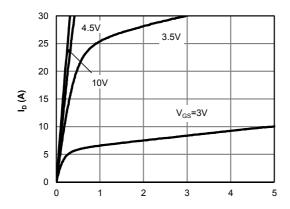

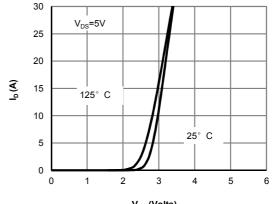

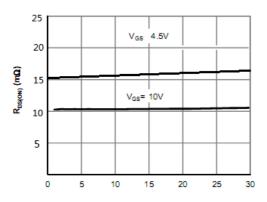

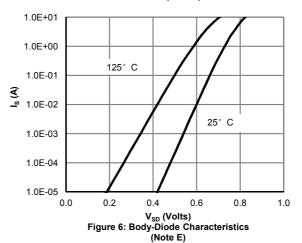

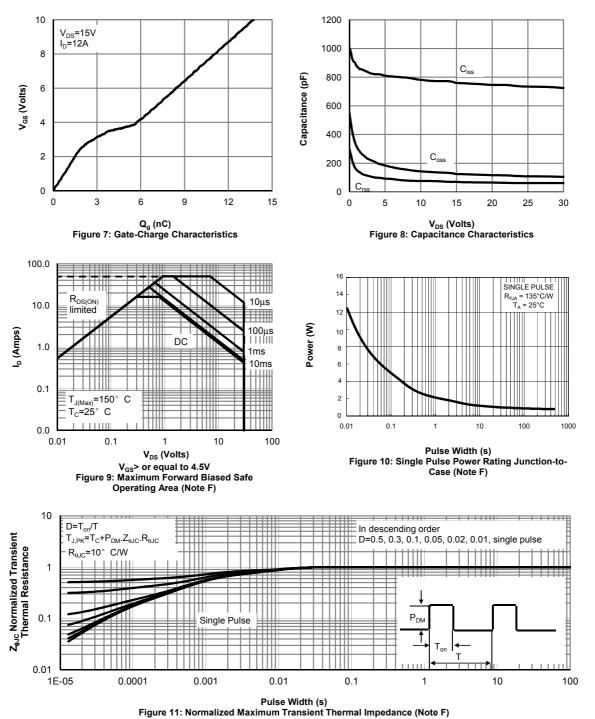

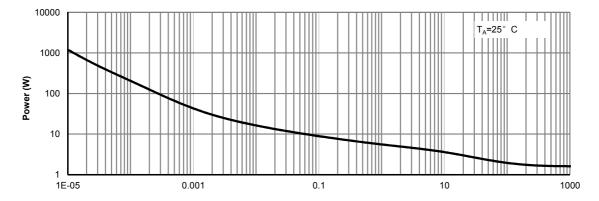

C. Single pulse width limited by junction temperature  $T_{J(MAX)}$ =150° C. D. The  $R_{BJA}$  is the sum of the thermal impedance from junction to case  $R_{BJC}$  and case to ambient. E. The static characteristics in Figures 1 to 6 are obtained using <300 $\mu$ s pulses, duty cycle 0.5% max.

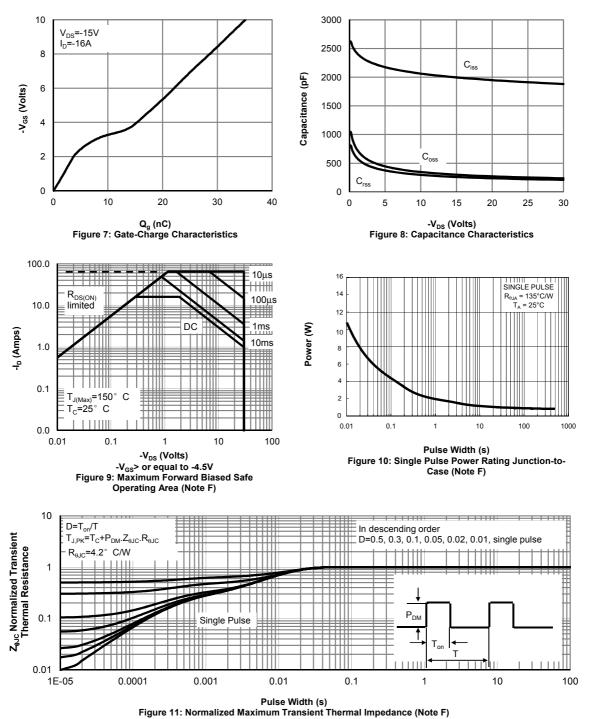

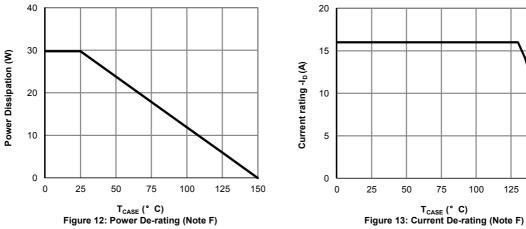

F. These curves are based on the junction-to-case thermal impedance which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of T<sub>J(MAX)</sub>=150° C. The SOA curve provides a single pulse rating.

G. The maximum current rating is package limited.

H. These tests are performed with the device mounted on 1 in<sup>2</sup> FR-4 board with 2oz. Copper, in a still air environment with T<sub>A</sub>=25° C.

V<sub>DS</sub> (Volts) Figure 1: On-Region Characteristics (Note E)

V<sub>GS</sub> (Volts) Figure 2: Transfer Characteristics (Note E)

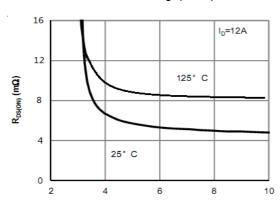

$\rm I_D$  (A) Figure 3: On-Resistance vs. Drain Current and Gate Voltage (Note E)

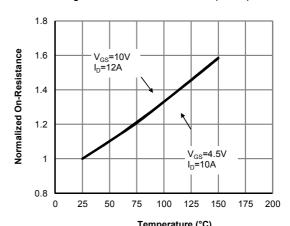

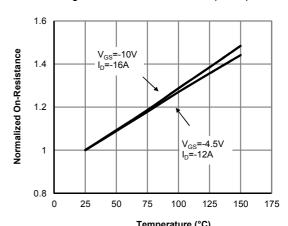

Temperature (°C)

Figure 4: On-Resistance vs. Junction Temperature

(Note E)

V<sub>GS</sub> (Volts)

Figure 5: On-Resistance vs. Gate-Source Voltage (Note E)

4

$T_{\text{CASE}} \, (^{\circ} \, \, \text{C}) \\ \text{Figure 12: Power De-rating (Note F)} \\ T_{\text{CASE}} \, (^{\circ} \, \, \text{C}) \\ \text{Figure 13: Current De-rating (Note F)}$

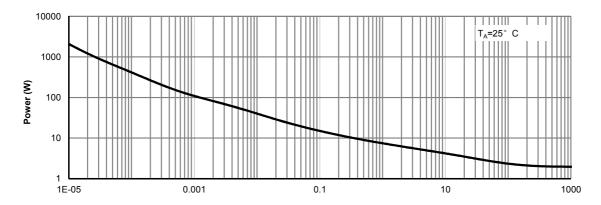

Pulse Width (s)

Figure 14: Single Pulse Power Rating Junction-to-Ambient (Note H)

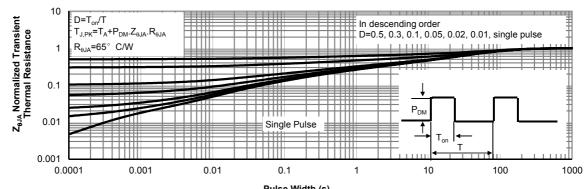

Pulse Width (s)

Figure 15: Normalized Maximum Transient Thermal Impedance (Note H)

5

#### Q2 Electrical Characteristics (T<sub>J</sub>=25°C unless otherwise noted)

| Symbol                 | Parameter                          | Conditions                                                        | Min  | Тур  | Max  | Units |

|------------------------|------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| STATIC F               | PARAMETERS                         |                                                                   |      |      |      |       |

| BV <sub>DSS</sub>      | Drain-Source Breakdown Voltage     | $I_D$ =-250 $\mu$ A, $V_{GS}$ =0V                                 | -30  |      |      | V     |

| I <sub>DSS</sub>       | Zero Gate Voltage Drain Current    | V <sub>DS</sub> = -30V, V <sub>GS</sub> =0V                       |      |      | -1   | μA    |

| DSS                    | Zero Gate Voltage Drain Gurrent    | T <sub>J</sub> =                                                  | 55°C |      | -5   | μΛ    |

| I <sub>GSS</sub>       | Gate-Body leakage current          | $V_{DS}$ =0V, $V_{GS}$ =±20V                                      |      |      | ±100 | nA    |

| $V_{GS(th)}$           | Gate Threshold Voltage             | $V_{DS}=V_{GS}$ , $I_{D}=-250\mu A$                               | -1.0 | -1.5 | -2.5 | V     |

|                        |                                    | V <sub>GS</sub> =-10V, I <sub>D</sub> =-5A                        |      | 10.5 | 14   | mΩ    |

| R <sub>DS(ON)</sub>    | Static Drain-Source On-Resistance  | T <sub>J</sub> =12                                                | 25°C | 15   | 19   | 11152 |

|                        |                                    | $V_{GS}$ =-4.5V, $I_D$ =-5A                                       |      | 17   | 20   | mΩ    |

| <b>g</b> <sub>FS</sub> | Forward Transconductance           | $V_{DS}$ =-5V, $I_D$ =-5A                                         |      | 43   |      | S     |

| $V_{SD}$               | Diode Forward Voltage              | I <sub>S</sub> =-1A, V <sub>GS</sub> =0V                          |      | -0.7 | -1.3 | V     |

| I <sub>S</sub>         | Maximum Body-Diode Continuous Cur  | rent <sup>G</sup>                                                 |      |      | -20  | Α     |

| DYNAMIC                | PARAMETERS                         |                                                                   |      |      |      |       |

| C <sub>iss</sub>       | Input Capacitance                  |                                                                   |      | 1125 |      | pF    |

| Coss                   | Output Capacitance                 | $V_{GS}$ =0V, $V_{DS}$ =-15V, f=1MHz                              |      | 201  |      | pF    |

| C <sub>rss</sub>       | Reverse Transfer Capacitance       |                                                                   |      | 86   |      | pF    |

| $R_g$                  | Gate resistance                    | f=1MHz                                                            |      | 4.5  | 9    | Ω     |

| SWITCHI                | NG PARAMETERS                      |                                                                   |      |      |      |       |

| $Q_g(10V)$             | Total Gate Charge                  |                                                                   |      | 18   | 25   | nC    |

| Q <sub>g</sub> (4.5V)  | Total Gate Charge                  | V <sub>GS</sub> =-10V, V <sub>DS</sub> =-15V, I <sub>D</sub> =-8A | 1    | 12   | 18   | nC    |

| $Q_{gs}$               | Gate Source Charge                 | VGS-10V, VDS-10V, ID-0/                                           | `    | 5.7  |      | nC    |

| $Q_{gd}$               | Gate Drain Charge                  |                                                                   |      | 8.8  |      | nC    |

| t <sub>D(on)</sub>     | Turn-On DelayTime                  |                                                                   |      | 11   |      | ns    |

| t <sub>r</sub>         | Turn-On Rise Time                  | V <sub>GS</sub> =-10V, V <sub>DS</sub> =-15V, R <sub>L</sub> =0.  | 9Ω,  | 7.5  |      | ns    |

| $t_{D(off)}$           | Turn-Off DelayTime                 | $R_{GEN}$ =3 $\Omega$                                             |      | 43.5 |      | ns    |

| t <sub>f</sub>         | Turn-Off Fall Time                 |                                                                   |      | 17.5 |      | ns    |

| t <sub>rr</sub>        | Body Diode Reverse Recovery Time   | $I_F$ =-16A, di/dt=500A/ $\mu$ s                                  |      | 13.3 |      | ns    |

| Q <sub>rr</sub>        | Body Diode Reverse Recovery Charge | l <sub>F</sub> =-16A, di/dt=500A/μs                               |      | 20   |      | nC    |

A. The value of  $R_{\theta JA}$  is measured with the device mounted on 1in<sup>2</sup> FR-4 board with 2oz. Copper, in a still air environment with  $T_A$  =25° C. The Power dissipation P<sub>DSM</sub> is based on R <sub>θJA</sub> t≤ 10s and the maximum allowed junction temperature of 150° C. The value in any given application depends on the user's specific board design.

6

B. The power dissipation  $P_D$  is based on  $T_{J(MAX)}$ =150° C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.

C. Single pulse width limited by junction temperature  $T_{J(MAX)}$ =150° C.

D. The R<sub>BJA</sub> is the sum of the thermal impedance from junction to case R<sub>BJC</sub> and case to ambient.

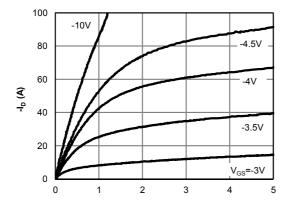

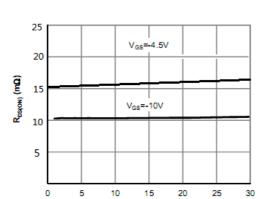

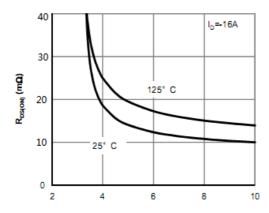

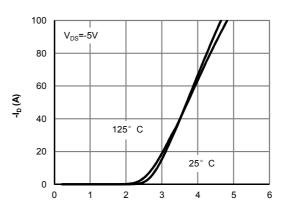

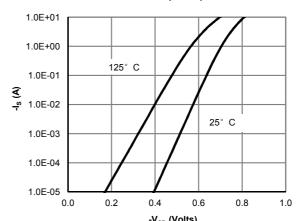

E. The static characteristics in Figures 1 to 6 are obtained using <300μs pulses, duty cycle 0.5% max.

F. These curves are based on the junction-to-case thermal impedance which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of T<sub>J(MAX)</sub>=150° C. The SOA curve provides a single pulse rating.

G. The maximum current rating is package limited.

H. These tests are performed with the device mounted on 1 in² FR-4 board with 2oz. Copper, in a still air environment with T<sub>A</sub>=25° C.

$\hbox{-V}_{\rm DS} \mbox{ (Volts)}$  Figure 1: On-Region Characteristics (Note E)

-I<sub>D</sub> (A) Figure 3: On-Resistance vs. Drain Current and Gate Voltage (Note E)

-V<sub>GS</sub> (Volts)

Figure 5: On-Resistance vs. Gate-Source Voltage (Note E)

-V<sub>GS</sub> (Volts) Figure 2: Transfer Characteristics (Note E)

Temperature (°C)

Figure 4: On-Resistance vs. Junction Temperature

(Note E)

-V<sub>SD</sub> (Volts) Figure 6: Body-Diode Characteristics (Note E)

www.mtsemi.com

7

8

125

150

Pulse Width (s)

Figure 14: Single Pulse Power Rating Junction-to-Ambient (Note H)

Pulse Width (s)

Figure 15: Normalized Maximum Transient Thermal Impedance (Note H)

9

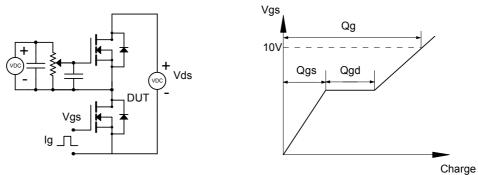

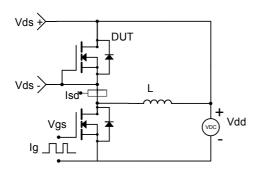

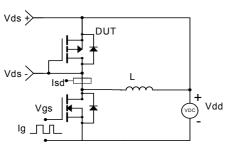

Figure A: Gate Charge Test Circuit & Waveforms

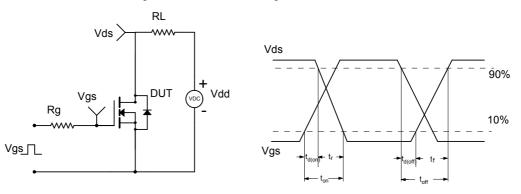

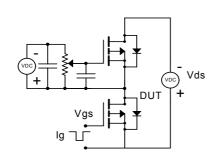

Figure B: Resistive Switching Test Circuit & Waveforms

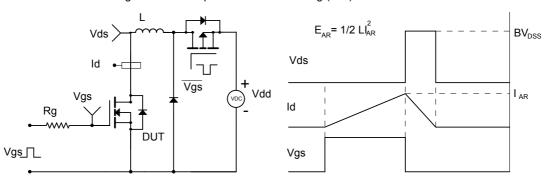

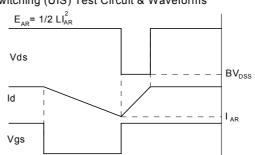

Figure C: Unclamped Inductive Switching (UIS) Test Circuit & Waveforms

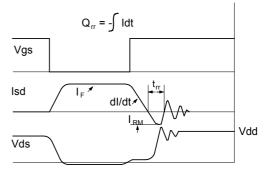

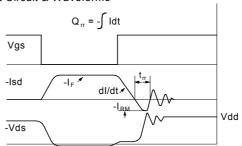

Figure D: Diode Recovery Test Circuit & Waveforms

## Gate Charge Test Circuit & Waveform

## Resistive Switching Test Circuit & Waveforms

## Unclamped Inductive Switching (UIS) Test Circuit & Waveforms

## Diode Recovery Test Circuit & Waveforms

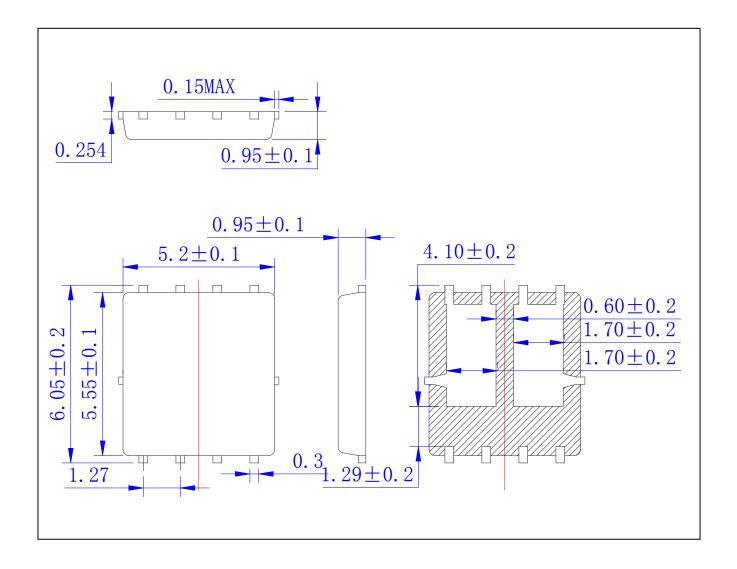

# DFN5×6 OUTLINE

#### Notes regarding these materials

- This document is provided for reference purposes only so that Mos-tech customers may select the appropriate

Mos-tech products for their use. Mos-tech neither makes warranties or representations with respect to the

accuracy or completeness of the information contained in this document nor grants any license to any

intellectual property rights or any other rights of Mos-tech or any third party with respect to the information in

this document.

- 2. Mos-tech shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Mos-tech products listed in this document, please confirm the latest product information with a Mos-tech sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Mos-tech such as that disclosed through our website. (http://www.mtsemi.com)

- Mos-tech has used reasonable care in compiling the information included in this document, but Mos-tech

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information

included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Mos-tech makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Mos-tech products.

- 7. With the exception of products specified by Mos-tech as suitable for automobile applications, Mos-tech products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Mos-tech sales office beforehand. Mos-tech shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Mos-tech products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Mos-tech shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Mos-tech products in any of the foregoing applications shall indemnify and hold harmless Mos-tech Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Mos-tech, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Mos-tech shall have no liability for malfunctions or damages arising out of the use of Mos-tech products beyond such specified ranges.

- 10. Although Mos-tech endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Mos-tech product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Mos-tech products listed in this document are detached from the products to which the Mos-tech products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Mos-tech products may not be easily detached from your products. Mos-techshall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Mos-tech.

- 13. Please contact a Mos-tech sales office if you have any questions regarding the information contained in this document, Mos-tech semiconductor products, or if you have any other inquiries.

## 注意

本文只是参考译文,前页所载英文版"Cautions"具有正式效力。

#### 关于利用本资料时的注意事项

- 本资料是为了让用户根据用途选择合适的本公司产品的参考资料,对于本资料中所记载的技术信息,并非意味着对本公司或者第三者的知识产权及其他权利做出保证或对实施权力进行的承诺。

- 2. 对于因使用本资料所记载的产品数据、图、表、程序、算法及其他应用电路例而引起的损害或者对第三者的知识产权及其他权利造成侵犯,本公司不承担任何责任。

- 不能将本资料所记载的产品和技术用于大规模破坏性武器的开发等目的、军事目的或其他的军需用途方面。 另外,在出口时必须遵守中国的《外汇及外国贸易法》及其他出口的相关法令并履行这些法令中规定的必要 手续。

- 4. 本资料所记载的产品数据、图、表、程序、算法以及其他应用电路例等所有信息均为本资料发行时的内容,本公司有可能在未做事先通知的情况下,对本资料所记载的产品或者产品规格进行更改。所以在购买和使用本公司的半导体产品之前,请事先向本公司的营业窗口确认最新的信息并经常留意本公司通过公司主页(http://www.mtsemi.com)等公开的最新信息。

- 对于本资料中所记载的信息,制作时我们尽力保证出版时的精确性,但不承担因本资料的叙述不当而致使顾客遭受损失等的任何相关责任。

- 6. 在使用本资料所记载的产品数据、图、表等所示的技术内容、程序、算法及其他应用电路例时,不仅要对所使用的技术信息进行单独评价,还要对整个系统进行充分的评价。请顾客自行负责,进行是否适用的判断。本公司对于是否适用不负任何责任。

- 7. 本资料中所记载的产品并非针对万一出现故障或是错误运行就会威胁到人的生命或给人体带来危害的机器、系统(如各种安全装置或者运输交通用的、医疗、燃烧控制、航天器械、核能、海底中继用的机器和系统等)而设计和制造的,特别是对于品质和可靠性要求极高的机器和系统等(将本公司指定用于汽车方面的产品用于汽车时除外)。如果要用于上述的目的,请务必事先向本公司的营业窗口咨询。另外,对于用于上述目的而造成的损失等,本公司概不负责。

- 8. 除上述第7项内容外,不能将本资料中记载的产品用于以下用途。如果用于以下用途而造成的损失,本公司概不负责。

- 1) 生命维持装置。

- 2) 植埋于人体使用的装置。

- 3) 用于治疗(切除患部、给药等)的装置。

- 4) 其他直接影响到人的生命的装置。

- 9. 在使用本资料所记载的产品时,对于最大额定值、工作电源电压的范围、放热特性、安装条件及其他条件请在本公司规定的保证范围内使用。如果超出了本公司规定的保证范围使用时,对于由此而造成的故障和出现的事故,本公司将不承担任何责任。

- 10. 本公司一直致力于提高产品的质量和可靠性,但一般来说,半导体产品总会以一定的概率发生故障、或者由于使用条件不同而出现错误运行等。为了避免因本公司的产品发生故障或者错误运行而导致人身事故和火灾或造成社会性的损失,希望客户能自行负责进行冗余设计、采取延烧对策及进行防止错误运行等的安全设计(包括硬件和软件两方面的设计)以及老化处理等,这是作为机器和系统的出厂保证。特别是单片机的软件,由于单独进行验证很困难,所以要求在顾客制造的最终的机器及系统上进行安全检验工作。

- 11. 如果把本资料所记载的产品从其载体设备上卸下,有可能造成婴儿误吞的危险。顾客在将本公司产品安装到顾客的设备上时,请顾客自行负责将本公司产品设置为不容易剥落的安全设计。如果从顾客的设备上剥落而造成事故时,本公司将不承担任何责任。

- 12. 在未得到本公司的事先书面认可时,不可将本资料的一部分或者全部转载或者复制。

- 13. 如果需要了解关于本资料的详细内容,或者有其他关心的问题,请向本公司的营业窗口咨询。

#### Keep safety first in your circuit designs!

1. MOS-TECH Semiconductor Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.